2024.11.07

2024.11.07

近日,控制器研究室成功研制出基于CPU+FPGA的EtherCAT主站控制器产品。EtherCAT通信协议是一种工业实时以太网协议,协议栈工作在以太网的数据链路层及以下,具有高达90%的带宽利用率。数据报文从主站出发,在经过每一个从站时使用ESC硬件芯片进行高速数据交换,使得通信系统具有高实时性和拓扑灵活等特点。随着运动控制领域的快速发展,基于EtherCAT通信协议的总线控制器成为研究热点,特别是一些对实时性和控制抖动要求比较高的场景,例如人形机器人、四足机器人和工业自动化生产线等场景。

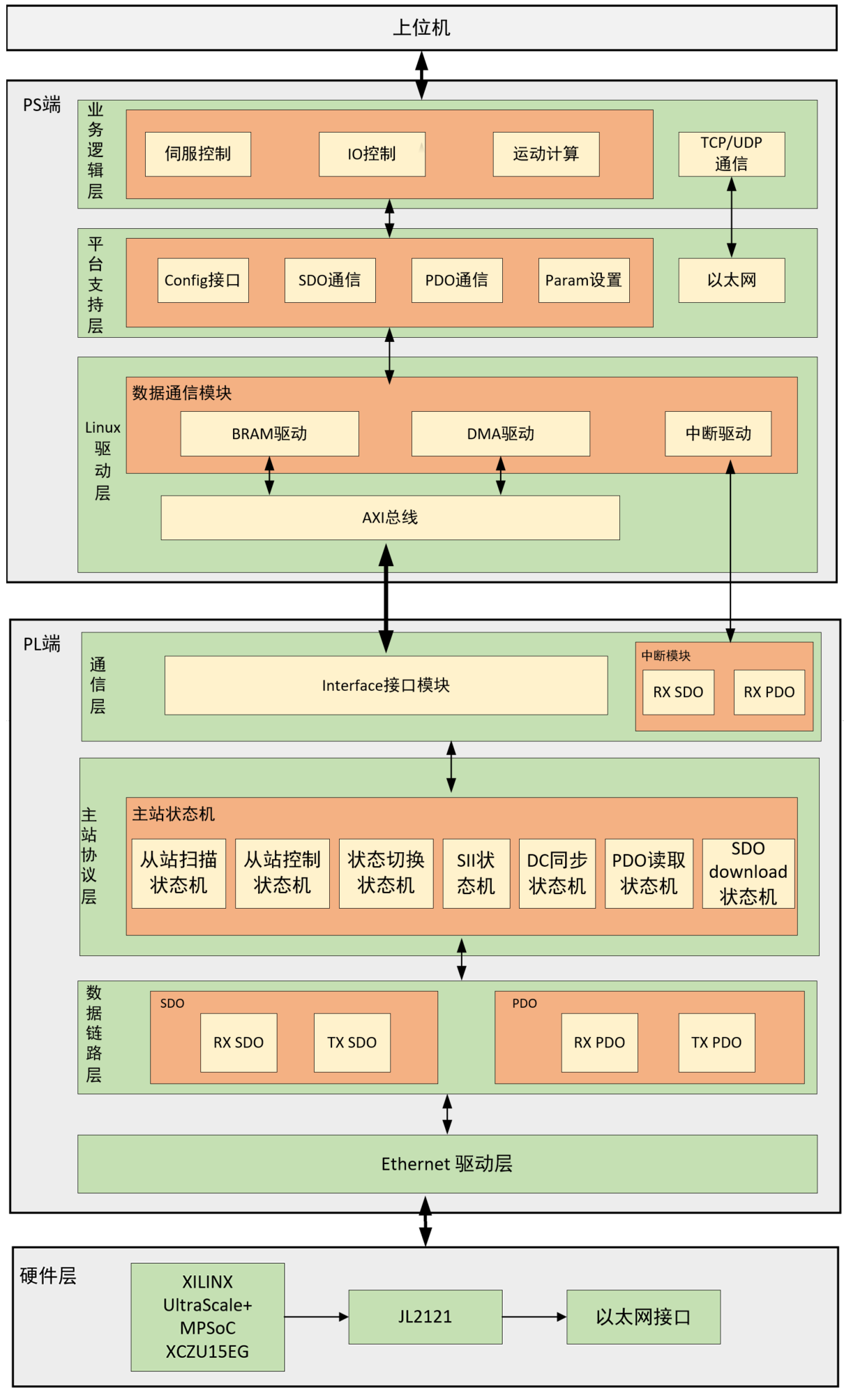

该自研控制器基于CPU+FPGA的异构方案,硬件平台可分为处理器系统部分Processor System(PS)和可编程逻辑部分Programmable Logic(PL)。PS端具有四核ARM Cortex-A53,部署应用层代码,实现主站对从站控制的业务逻辑,同时使用AXI总线实现PS端与PL端间的数据通信交互;PL端部署EtherCAT协议栈的RTL逻辑代码,主要实现EtherCAT协议栈的初始化、状态机跳转、SDO通信、PDO通信、DC同步等功能,在PL端挂载有一路以太网MAC,硬件引出连接以太网物理收发器,作为EtherCAT主站的物理网口使用。

该控制器利用FPGA高精度时钟、并行处理等优势,通信带宽高达100Mbps,实现低至31.25us的通信周期,周期抖动小于±250ns,DC同步精度小于±1us,支持SDO/PDO通信功能。较传统的EtherCAT软件主站,进一步提升了控制精度并缩短了控制周期,对实时性要求高的高频运动控制领域有着广阔的应用前景和极高的经济效益。

0551-65387203

0551-65387203

jhzx@jhatc.cn

jhzx@jhatc.cn

安徽省合肥市高新技术开发区望江路920号 中安创谷科技园二期H3—H8幢

安徽省合肥市高新技术开发区望江路920号 中安创谷科技园二期H3—H8幢